封装技术演进:小型化、高功率、高能效

器件小型化、大功率应用、高能效

功率半导体封装技术

封装技术——超大超薄芯片无损剥离技术

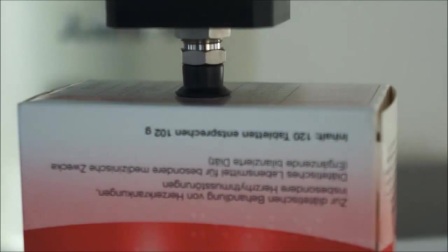

目前业界广泛使用的芯片已从120um发展到40um,可以降低热阻,提高散热性能,降低能耗。 但薄芯片容易弯曲、断裂,焊头真空拾取过程中容易掉落芯片,严重影响芯片拾取效率。

(1)力控多顶针无损剥离顶晶装置

力控多顶针剥离顶晶装置,顶晶装置上装有力控组件,实时监控,保证顶晶过程中顶针施力稳定,力控制精度高,从而实现超薄大型芯片的高效率和高可靠性。 条。

(2)柔性拾取焊头装置

在薄芯片的取放过程中,需要控制焊头的压力,以防止芯片被压坏。 灵活的拾取焊头+特殊结构的吸嘴,有助于顺利拾取薄切屑。

核心技术——多兼容自动送料技术

IGBT常用的安装工艺有两种,一种是焊膏工艺包装技术与设备,另一种是焊接芯片工艺。 目前,该设备无法同时兼容这两种功能。

多兼容自动送料装置,兼容Wafer、Tary三种送料方式。 可方便地完成自动切换、自动上下料,操作简单,工作效率高。

核心技术——高精度视觉检测技术

传统算法:首先对缺陷芯片图像进行增强,然后进行均值滤波,最后以处理后图像的灰度为基准和设定的参考值对原始图像进行动态阈值处理。 检测精度满足3um要求,但不适合单个芯片复杂表面区域的缺陷检测。

高精度微缺陷检测技术:首先利用矩形灰度值结构元素对图像进行闭运算,然后将处理后的图像从原始图像中减去,最后利用阈值对缺陷进行分割。 检测精度为3um±0.5um,可检测复杂背景表面的缺陷。

在芯片视觉检测领域,缺陷检测精度要求为3um±0.5um。 传统的算法思路是首先对缺陷芯片图像进行增强,然后进行均值滤波,最后以处理后图像的灰度为基准和设定的参考值对原始图像进行动态阈值处理。 该算法在检测芯片光滑背景表面的缺陷时具有良好的稳定性,检测精度完全满足3um要求。 然而,它不适合单个芯片复杂表面区域的缺陷检测。

它利用深度学习算法处理技术,首先利用矩形灰度值结构元素对图像进行闭运算,然后将处理后的图像从原始图像中减去。 最后,使用阈值对缺陷进行分割。 该技术不仅可以检测光滑背景表面的缺陷,还可以检测复杂背景表面的缺陷,检测精度为3um±0.5um。

核心技术——基于通信的高速运动控制系统

该控制系统响应度高,可以缩短运动周期,提高设备的工作效率,更好地满足客户的需求包装技术与设备,使设备具有优异的市场竞争力。

功率半导体封装关键技术公共服务平台

先进外延平台(张家港分平台)

纳米加工平台(苏州总部6英寸微纳加工线)

集成微系统封装平台(苏州总部6英寸微纳加工线

微纳加工平台(南昌分公司)

纳米加工平台(广东(佛山)子平台)

01

02

中国科学院苏州纳米技术研究所南昌研究院微纳加工平台(南昌)是集微纳器件封装、测试和可靠性失效分析于一体的公共开放平台,设备先进,服务模式特色。

集封装、测试、可靠性、失效分析检测于一体,先进、有特色、具有应用基础和应用前景的半导体芯片封装测试基地。

拥有微纳电子器件、光电器件、光机系统、生物传感器和生物芯片开发等多方面的封装和测试能力。

布局和发展WLP(晶圆级封装)、3D封装、SIP(系统级封装)等先进封装领域

具有孵化器功能,为企业提供全方位开放服务体系。

目前已建成4000㎡公共开放式超净实验室和1000㎡科研实验室,相关设备50余台套,总价值超过3000万元,团队60余人研发服务人员。 获批:江西省内外共建创新平台、江西省新型研发机构、江西省产业集群公共服务平台、南昌市服务外包重点公共服务平台、南昌市先进封装测试重点实验室等。

功率半导体封装设备国产化

我国贴片设备几乎全部被国外品牌垄断,国产化程度较低。 贴片设备国产化率不超过5%。

就利基领域的IGBT芯片贴装设备而言,国内市场主要被Besi和AG垄断。

贴片设备正处于快速增长时期。 发展国产高端贴片设备势在必行,国产替代空间巨大。 通过此次实施,可填补半导体封装设备领域的国内空白,实现进口替代。 对于推动我国功率半导体产业升级、提高我国半导体产业国际竞争力具有重要意义。